Let%27s delve into the differences between hard IP and soft IP in the context of System on a Chip (SoC) design:

1. Hard IP:

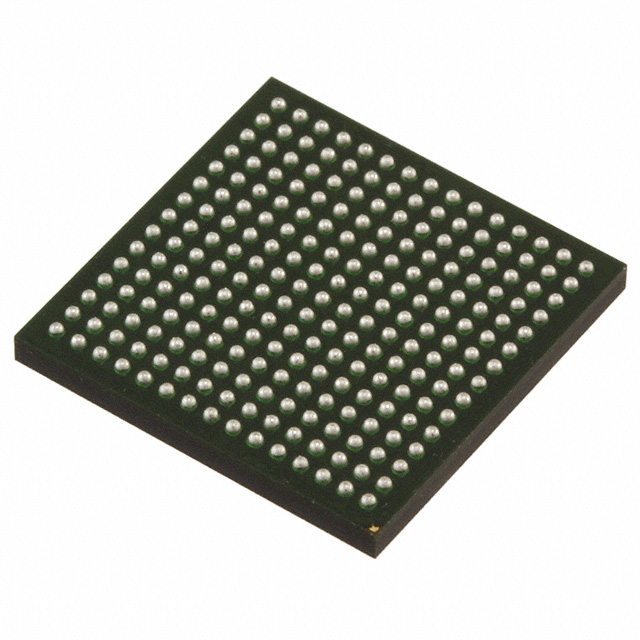

- Definition: Hard IP refers to circuitry that is hard-wired and etched into silicon during the manufacturing process. It is designed to perform specific functions and is optimized for efficiency, speed, and area.

- Characteristics:

- Fixed Functionality: Hard IP blocks are designed for a single purpose and cannot be reconfigured or modified.

- Technology-Dependent: They are tightly coupled to the process technology used for fabrication.

- High Performance: Hard IP is optimized for performance, often using dedicated hardware resources.

- Examples of hard IP include processors, DSP blocks, and high-speed transceivers.

- Efficient and Fast: Hard IP is streamlined, with minimal overhead.

- Less Flexible: It lacks the flexibility of reconfiguration.

- Not Portable: Hard IP is specific to a particular process node and vendor.

- Examples: The core and peripherals in a microcontroller or processor are typically hard IP¹⁴.

2. Soft IP:

- Definition: Soft IP consists of functional descriptions written in hardware description languages (such as Verilog or VHDL). It is synthesized into logic elements during the design process.

- Characteristics:

- Configurable: Soft IP can be customized and reconfigured to suit different applications.

- Technology-Independent: It is not tied to a specific process technology.

- RTL Cores: Soft IP includes synthesizable RTL (Register Transfer Level) models.

- Flexibility: Designers can modify and adapt soft IP to meet specific requirements.

- Verification Required: Soft IP must undergo synthesis and verification before implementation.

- Examples: Soft IP includes communication interfaces, memory controllers, and custom logic.

- Portable: It can be used across different process nodes and vendors.

- More Versatile: Soft IP is suitable for various applications¹⁵.

In summary, hard IP provides fixed, efficient functionality but lacks flexibility, while soft IP is configurable, technology-independent, and adaptable to different designs. Designers choose between them based on specific project requirements and trade-offs¹⁴⁵. ️<br>

(1) Whats the difference between Soft IP and Hard IP in FPGA?. https://electronics.stackexchange.com/questions/495065/whats-the-difference-between-soft-ip-and-hard-ip-in-fpga.

(2) It’s All IP In An SoC - Semiconductor Engineering. https://semiengineering.com/its-all-ip-in-an-soc/.

(3) System-on-Chip (SoC) Design Elements Guide | Synopsys Cloud. https://www.synopsys.com/cloud/insights/system-on-chip-design.html.

(4) SoC: A Real Platform for IP Reuse, IP Infringement, and IP ... - Hindawi. https://www.hindawi.com/journals/vlsi/2011/731957/.

(5) IP and VIPs in VLSI SOC Designs - Usage and Differences. https://verificationexcellence.in/ip-and-vips-in-vlsi-design/.

(6) Choosing an Intellectual Property Core - Amazon Web Services, Inc.. https://s3-eu-west-1.amazonaws.com/downloads-mips/mips-documentation/choosing_an_intellectual_property_core.pdf.

icDirectory United Kingdom | https://www.icdirectory.co.uk/a/blog/what-is-the-difference-between-hard-ip-and-soft-ip-in-soc-design.html