## Design Trade-Offs Between Size and Efficiency in PMIC Packages

In PMIC design, package size and efficiency are closely interrelated, and optimizing both simultaneously requires careful consideration of thermal, electrical, and mechanical constraints. Trade-offs between miniaturization and efficiency are inevitable due to physical limits of power dissipation, component placement, and parasitic effects.

## 1. Thermal Constraints

* Heat Dissipation:

* Smaller packages have less surface area and lower thermal mass, limiting their ability to dissipate heat generated by switching and conduction losses.

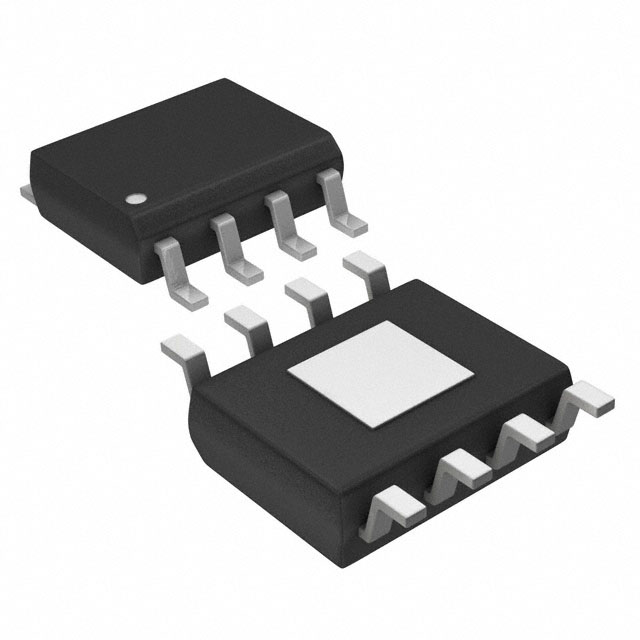

* High-efficiency PMICs often require larger packages or exposed pads to conduct heat to the PCB or a heatsink.

* Thermal Impedance:

* Thermal resistance (θJA, θJC) increases as package size decreases, leading to higher junction temperatures for a given power loss, which can degrade efficiency and reliability.

* Trade-Off:

* Reducing package size often forces designers to tolerate higher junction temperatures or to limit output current to maintain safe operation, which can reduce efficiency in high-load conditions.

## 2. Conduction Losses and Package Parasitics

* MOSFET R_DS(on) Limitations:

* Smaller packages can only accommodate smaller die or fewer parallel MOSFETs, increasing series resistance and conduction losses.

* Higher conduction losses reduce overall efficiency, especially in high-current applications.

* Inductor Integration Constraints:

* Some PMICs integrate inductors on-chip or in-package (e.g., LGA embedded inductors). Smaller packages limit inductance values, which can increase peak-to-peak ripple and switching losses.

* Parasitic Effects:

* Package parasitic inductance and capacitance increase with compact designs, affecting switching transients and potentially reducing efficiency at high frequencies.

## 3. Switching Frequency vs. Package Size

* High-Frequency Operation:

* To reduce inductor and capacitor size, designers may increase switching frequency.

* Higher frequency increases switching losses (gate charging, MOSFET transitions, and diode losses), which can offset the benefits of a smaller package.

* Trade-Off:

* Miniaturization may force higher switching frequencies, which reduces component size but reduces efficiency, especially under medium-to-high load.

## 4. Output Current Handling

* Current Density:

* Smaller packages have narrower traces and fewer pins for current conduction.

* High-current PMICs in small packages may experience higher IR drops and increased losses in both the package and PCB traces.

* Derating:

* To prevent excessive heating, designers often derate maximum output current in smaller packages, which can limit system performance and efficiency under peak loads.

## 5. Capacitor and Decoupling Limitations

* Output Filtering:

* Reduced package footprint may constrain the number or size of decoupling capacitors placed close to the PMIC.

* Less capacitance or higher ESR increases output ripple and can require higher switching duty cycles, indirectly lowering efficiency.

* Integrated Capacitors:

* Some advanced PMICs embed small ceramic capacitors in-package, but these often provide limited capacitance compared to discrete external capacitors, affecting efficiency under dynamic load conditions.

## 6. Cost and Reliability Considerations

* Miniaturization Costs:

* High-efficiency small packages often require advanced packaging techniques (e.g., flip-chip, embedded inductors, multi-layer substrates), increasing cost.

* Thermal Stress on Solder Joints:

* High-power density in small packages increases junction temperature and thermal cycling stress, potentially impacting long-term efficiency due to degradation of materials.

## 7. Multi-Phase Integration Trade-Offs

* Phase Count vs. Package Size:

* Multi-phase buck converters reduce ripple and improve efficiency at high currents.

* Integrating multiple phases in a small package is challenging due to limited pin count and thermal dissipation, potentially reducing the number of phases and hence efficiency under high load.

## 8. Summary of Key Trade-Offs

| Parameter | Effect of Smaller Package | Impact on Efficiency |

| ----------------------------- | --------------------------------------- | ---------------------------------------------------------- |

| Thermal Dissipation | Reduced surface area | Higher junction temperature → lower efficiency |

| MOSFET Conduction Loss | Fewer parallel MOSFETs possible | Higher R_DS(on) → increased losses |

| Switching Frequency | May need higher frequency | Higher switching losses → lower efficiency |

| Output Current Capacity | Limited by trace width and pin count | May require derating → reduced efficiency at peak loads |

| Decoupling/Output Capacitance | Fewer capacitors or smaller capacitance | Increased ripple and switching stress → reduced efficiency |

| Multi-phase Integration | Fewer phases possible | Less ripple cancellation → lower overall efficiency |

## Conclusion

The design trade-offs between size and efficiency in PMIC packages involve balancing:

* Thermal management capabilities against package footprint.

* Conduction and switching losses versus die and MOSFET size.

* Switching frequency and filter components versus available PCB and package space.

* Maximum current delivery and ripple control versus miniaturization limits.

In practice, achieving high efficiency in small PMIC packages requires careful selection of MOSFETs, die size, thermal pads, switching frequency, and system-level PCB design. Designers must weigh these trade-offs according to target load profiles, thermal constraints, and mechanical requirements, often compromising either ultimate miniaturization or peak efficiency.

icDirectory United Kingdom | https://www.icdirectory.co.uk/a/blog/what-are-the-design-trade-offs-between-size-and-efficiency-in-pmic-packages.html